# MIPS32® 24KEc<sup>TM</sup> Processor Core Datasheet

**December 14, 2005**

The MIPS32® 24KEc<sup>TM</sup> core from MIPS Technologies is a high-performance, low-power, 32-bit MIPS RISC core designed for custom system-on-silicon applications. The core is designed for semiconductor manufacturing companies, ASIC developers, and system OEMs who want to rapidly integrate their own custom logic and peripherals with a high-performance RISC processor. Fully synthesizable and highly portable across processes, it can be easily integrated into full system-on-silicon designs, allowing developers to focus their attention on end-user products.

The 24KEc core implements the MIPS32 Release 2 Architecture in an 8-stage pipeline. It includes support for the MIPS16e<sup>TM</sup> application specific extension and the 32-bit privileged resource architecture. This standard architecture allows support by a wide range of industry standard tools and development systems.

The 24KEc core incorporates the DSP Application Specific Extension (ASE), providing support for a number of powerful data processing operations. There are instructions for executing fractional arithmetic (Q15/Q31) and for saturating arithmetic. Additionally, for smaller data sizes, SIMD operations are supported, allowing 2x16b or 4x8b operations to occur simultaneously. Another feature of the ASE is the inclusion of additional HI/LO accumulator registers to improve the parallelization of independent accumulation routines.

To maintain high pipeline utilization, dynamic branch prediction is included in the form of a Branch History Table and a Return Prediction Stack. The Memory Management Unit (MMU) contains 4-entry instruction and 8-entry data Translation Lookaside Buffers (ITLB/DTLB) and a configurable 16/32/64 dual-entry joint TLB (JTLB) with variable page sizes. Alternatively, for applications not requiring address mapping or protection, the TLBs can be replaced with a simple Fixed Mapping mechanism.

The synthesizable 24KEc core includes a high performance Multiply/Divide Unit (MDU). The MDU is fully pipelined to support a single cycle repeat rate for 32x32 MAC instructions, which enables multiply-intensive algorithms to be performed efficiently. Further, in the 24KEc Pro<sup>TM</sup> Core, the optional CorExtend block can utilize the HI/LO registers in the MDU block. The CorExtend block allows specialized functions to be efficiently implemented.

Instruction and data level-one caches are configurable at 0, 8, 16, 32, or 64 KB in size. Each cache is organized as 4-way set associative. Data cache misses are non-blocking and up to 4 may be outstanding. Two instruction cache misses can be outstanding. Both caches are virtually indexed and physically tagged to allow them to be accessed in the same cycle that the address is translated. To achieve high frequencies while using commercially available SRAM generators, the cache access is spread across two pipeline stages, leaving nearly an entire cycle for the SRAM access.

The Bus Interface Unit implements the Open Core Protocol (OCP) which has been developed to address the needs of SOC designers. This implementation features 64-bit read and write data buses to efficiently transfer data to and from the L1 caches. The BIU also supports a variety of core/bus clock ratios to give greater flexibility for system design implementations.

Optional interfaces are supported to external scratchpad or coprocessor blocks.

An Enhanced JTAG (EJTAG) version 3.10 compliant block allows for software debugging of the processor and includes a TAP controller as well as optional instruction and data virtual address/value breakpoints. Additionally, real-time tracing of instruction program counter, data address and data values can be supported.

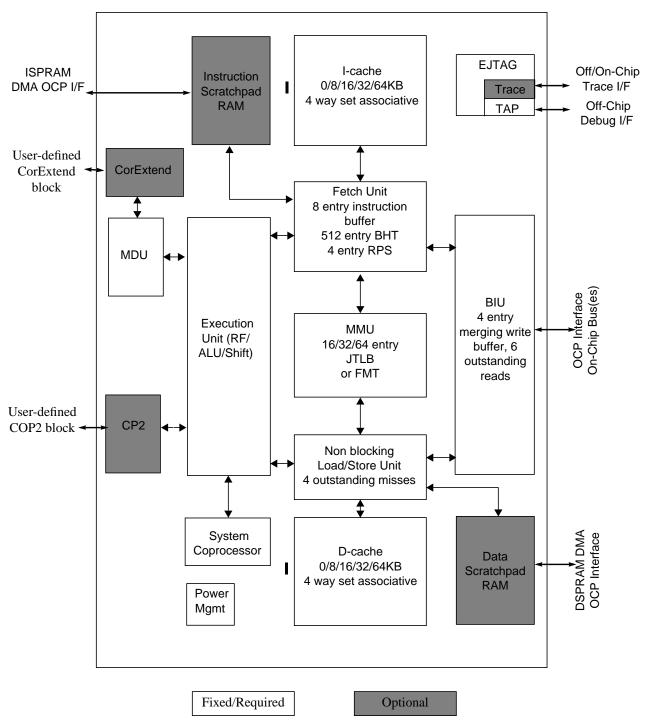

Figure 1 shows a block diagram of the 24KEc core.

Figure 1 24KEc<sup>TM</sup> Core Block Diagram

## 24KEc<sup>TM</sup> Core Features

- 8-stage pipeline

- 32-bit address paths

- 64-bit data paths to caches and external interface

- MIPS32-Compatible Instruction Set

- Multiply-Accumulate and Multiply-Subtract Instructions (MADD, MADDU, MSUB, MSUBU)

- Targeted Multiply Instruction (MUL)

- Zero/One Detect Instructions (CLZ, CLO)

- Wait Instruction (WAIT)

- Conditional Move Instructions (MOVZ, MOVN)

- Prefetch Instruction (PREF)

### • MIPS32 Enhanced Architecture (Release 2) Features

- Vectored interrupts and support for external interrupt controller

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow registers (optionally, one or three additional shadows can be added to minimize latency for interrupt handlers)

- Bit field manipulation instructions

- MIPS32 Privileged Resource Architecture

- MIPS DSP ASE

- Fractional data types (Q15, Q31)

- Saturating arithmetic

- SIMD instructions operate on 2x16b or 4x8b simultaneously

- 3 additional pairs of accumulator registers

- Programmable Memory Management Unit

- 16/32/64 dual-entry JTLB with variable page sizes

- 4-entry ITLB

- 8-entry DTLB

- Optional simple Fixed Mapping Translation (FMT) mechanism

# • MIPS16e<sup>TM</sup> Code Compression

- 16 bit encodings of 32 bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE & RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8 and 16 bit datatypes

- Programmable L1 Cache Sizes

- Individually configurable instruction and data caches

- Instruction and Data cache sizes of 0/8/16/32/64 KB

- 4-Way Set Associative

- Up to 4 outstanding load misses

- Write-back and write-through support

- 32-byte cache line size

- Virtually indexed, physically tagged

- Cache line locking support

- Non-blocking prefetches

- Optional parity support

### · Bus Interface

- OCP 2.1 compliant

- OCP interface with 32-bit address and 64-bit data

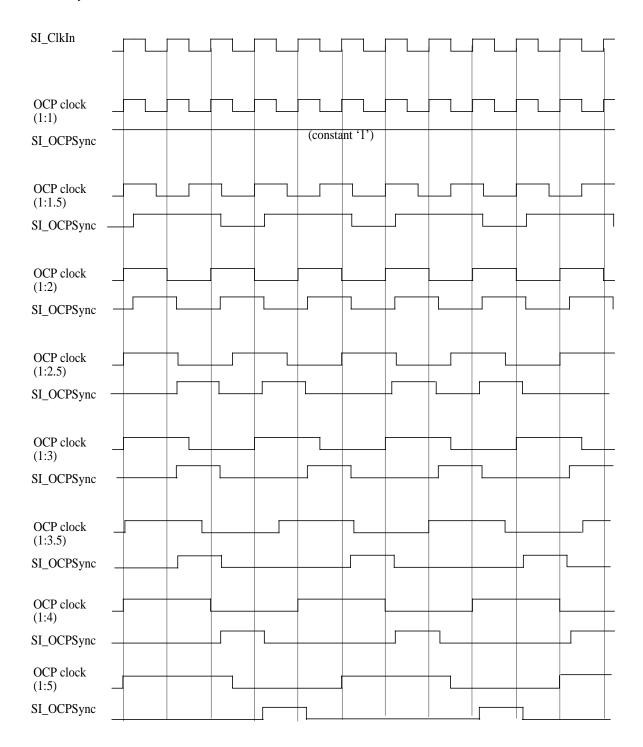

- OCP interface runs at core/bus clock ratios of 1, 1.5, 2,

2.5, 3, 3.5, 4 or 5 via a separate synchronous bus clock

- Handshaked interface to allow core/bus clock ratio to change without resetting the system

- Burst size of four 64-bit beats

- 4 entry write buffer

- "Simple" byte enable mode allows easier bridging to other bus standards

- Extensions for front-side L2 cache

## Scratchpad RAM support

- Independent Instruction and Data Scratchpad RAM

- Independent of cache configuration

- Independent 64 bit OCP interface for external DMA

- External interface runs at the same core/bus clock ratio as that of BIU interface

- Maximum size of 1MB each

- Interface allows back-stalling the core

### Multiply/Divide Unit

- Maximum issue rate of one 32x32 multiply per clock

- 5 cycle multiply latency

- Early-in iterative divide. Minimum 12 and maximum 38 clock latency (dividend (rs) sign extension-dependent)

## CorExtend<sup>TM</sup> User Defined Instruction Set Extensions (available in 24KEc Pro<sup>TM</sup> core)

- Allows user to define and add instructions to the core at build time

- Maintains full MIPS32 compatibility

- Supported by industry standard development tools

- Single or multi-cycle instructions

- Separately licensed; a core with this feature is known as the 24KEc Pro<sup>TM</sup> core

- Implemented in same block as MDU, allows all HI and LO registers to be shared for MIPS32 and CorExtend multiply operations.

### • Coprocessor 2 interface

- 64 bit interface to a user designed coprocessor

### Power Control

- Minimum frequency: 0 MHz

- Power-down mode (triggered by WAIT instruction)

- Support for software-controlled clock divider

- Support for extensive use of local gated clocks

### · EJTAG Debug

Support for single stepping

- Virtual instruction and data address/value breakpoints

- TAP controller is chainable for multi-CPU debug

- Cross-CPU breakpoint support

- EJTAG version 3.10 compliant

- · MIPS Trace

- PC, data address and data value tracing w/ trace compression

- Support for on-chip and off-chip trace memory

- PDTrace version 4.1 compliant

- · Testability

- Full scan design achieves test coverage in excess of 99% (dependent on library and configuration options)

- Optional memory BIST for internal SRAM arrays

### **Architecture Overview**

The 24KEc core contains a variety of blocks some of which are always present, while others are optional.

The required blocks are as follows:

- Fetch Unit

- · Execution Unit

- MIPS16e recode

- System Control Coprocessor (CP0)

- Memory Management Unit (MMU)

- Cache Controllers

- Bus Interface Unit (BIU)

- Power Management

- · Instruction Cache

## Optional blocks include:

- CorExtend<sup>TM</sup> User Defined Instruction (UDI) support

- Enhanced JTAG (EJTAG) breakpoints

- MIPS Trace (PDTrace) support

- Instruction/Data cache

- · Instruction/Data scratchpad

- · COP2 interface

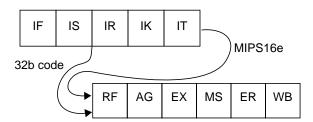

## **Pipeline Flow**

The 24KEc core implements an 8-stage pipeline. Three extra fetch stages are conditionally added when executing MIPS16e instructions. This pipeline allows the processor

to achieve a high frequency while maintaining reasonable area and power numbers.

The 24KEc core pipeline consists of the following stages:

- · IF Instruction Fetch First

- IS Instruction Fetch Second

- IR Instruction Recode (MIPS16e only)

- IK Instruction Kill (MIPS16e only)

- IT Instruction Fetch Third (MIPS16e only)

- RF Register File access

- · AG Address Generation

- EX Execute

- · MS Memory Second

- ER Exception Resolution

- WB WriteBack

The 24KEc core implements a bypass mechanism that allows the result of an operation to be forwarded directly to the instruction that needs it without having to write the result to the register and then read it back.

Figure 2 shows a diagram of the 24KEc core pipeline.

Figure 2 24KEc<sup>TM</sup> Core Pipeline

# **IF Stage: Instruction Fetch First**

- I-cache tag/data arrays accessed

- · Branch History Table accessed

- · ITLB address translation performed

- Instruction watch and EJTAG break compares done

#### IS - Instruction Fetch Second

- · Detect I-cache hit

- · Way select

- MIPS32 Branch prediction

#### IR - Instruction Recode

- MIPS16e instruction recode

- MIPS16e branch prediction

#### **IK - Instruction Kill**

• MIPS16e instruction kill

### **IT - Instruction Fetch Third**

- · Instruction Buffer

- · Branch target calculation

### RF - Register File Access

- Register File access

- Instruction decoding/dispatch logic

- Bypass muxes

### **AG - Address Generation**

- · D-cache Address Generation

- Bypass muxes

### EX - Execute/Memory Access

- · Skewed ALU

- DTLB

- · Start DCache access

- · Branch Resolution

- Data watch and EJTAG break address compares

### MS - Memory Access Second

- · Complete DCache access

- · DCache hit detection

- · Way select mux

- · Load align

- EJTAG break data value compare

# **ER- Exception Resolution**

- Instruction completion

- · Register file write setup

- Exception processing

#### WB - Writeback

Register file writeback occurs on rising edge of this cycle

# 24KEcTM Core Logic Blocks

The 24KEc core consists of the following logic blocks, shown in Figure 1. These logic blocks are defined in the following subsections:

- · Fetch Unit

- · Execution Unit

- · MIPS16e support

- System Control Coprocessor (CP0)

- Memory Management Unit (MMU)

- · Cache Controller

- Bus Interface Unit (BIU)

- · Power Management

## **Fetch Unit**

The 24KEc core fetch unit is responsible for fetching instructions and providing them to the rest of the pipeline, as well as handling control transfer instructions (branches, jumps, etc.). It calculates the address for each instruction fetch and contains an instruction buffer that decouples the fetching of instructions from their execution.

The fetch unit contains two structures for the dynamic prediction of control transfer instructions. A 512-entry Branch History Table (BHT) is used to predict the direction of branch instructions. It uses a bimodal algorithm with two bits of history information per entry. Also, a 4-entry Return Prediction Stack (RPS) is a simple structure to hold the return address from the most recent subroutine calls. The link address is pushed onto the stack whenever a JAL, JALR, or BGEZAL instruction is seen. Then that address is popped when a JR instruction occurs.

### **Execution Unit**

The 24KEc core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The 24KEc core contains thirty-two 32-bit general-purpose registers used for integer operations and address calculation. Optionally, one or three additional register file shadow sets (each containing thirty-two registers) can be added to minimize context switching overhead during interrupt/exception processing. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Logic for verifying branch prediction

- · Load aligner

- Bypass multiplexers used to avoid stalls when executing instructions streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bitwise logical operations

- Shifter & Store Aligner

The execution unit also includes the following DSP ASE operations for various data types:

- two-cycle add, sub, absolute, shift, compare

- two-cycle compare, byte manipulation, precision control

# MIPS16e<sup>TM</sup> Application Specific Extension

The 24KEc core includes support for the MIPS16e ASE. This ASE improves code density through the use of 16-bit encoding of many MIPS32 instructions plus some MIPS16e-specific instructions. PC relative loads allow quick access to constants. Save/Restore macro instructions provide for single instruction stack frame setup/teardown for efficient subroutine entry/exit.

### Multiply/Divide Unit (MDU)

The 24KEc core includes a multiply/divide unit (MDU) that contains a separate pipeline for integer multiply and divide operations. This pipeline operates in parallel with the integer unit pipeline and does not stall when the integer pipeline stalls. This allows any long-running MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The MDU consists of a pipelined 32x32 multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic.

The MDU supports execution of one multiply or multiply accumulate operation every clock cycle.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If rs is 8 bits

wide, 23 iterations are skipped. For a 16-bit-wide rs, 15 iterations are skipped, and for a 24-bit-wide rs, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes a pipeline stall until the divide operation is completed.

Table 1 lists the latencies (number of cycles until a result is available) and repeat rates (peak issue rate of cycles until the operation can be reissued) for the 24KEc core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks. For a more detailed discussion of latencies and repeat rates, refer to Chapter 2 of the MIPS32 24KE Processor Core Family Software User's Manual.

Table 1 24KEc<sup>TM</sup> Core Integer Multiply/Divide Unit Latencies and Repeat Rates

| Opcode                                   | Operand<br>Size<br>(mul <i>rt</i> )<br>(div <i>rs</i> ) | Latency | Repeat<br>Rate |

|------------------------------------------|---------------------------------------------------------|---------|----------------|

| MULT/MULTU,<br>MADD/MADDU,<br>MSUB/MSUBU | 32 bits                                                 | 5       | 1              |

| MUL                                      | 32 bits                                                 | 5       | 1 <sup>1</sup> |

|                                          | 8 bits                                                  | 12/14   | 12/14          |

| DIV/DIVU                                 | 16 bits                                                 | 20/22   | 20/22          |

| DIV/DIVO                                 | 24 bits                                                 | 28/30   | 28/30          |

|                                          | 32 bits                                                 | 36/38   | 36/38          |

1.If there is no data dependency, a MUL can be issued every cycle.

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the general-purpose register file.

In addition to the HI/LO targeted operations, the MIPS32 architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair.

Two other instructions, multiply-add (MADD) and multiply-subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and

LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

The MDU also implements various shift instructions operating on the HI/LO register and multiply instructions as defined in the DSP ASE. It supports all the data types required for this purpose and includes three extra HI/LO registers as defined by the ASE. The MDU also allows the CorExtend interface to access these HI/LO registers (24KEc Pro<sup>TM</sup> core only).

Table 2 lists the latencies and repeat rates for the DSP multiply and dot-product operations. The approximate latencies and repeat rates are listed in terms of pipeline clocks. For a more detailed discussion of latencies and repeat rates, refer to the MIPS32 24KEc Processor Core Family Software User's Manual.

Table 2 24KEc<sup>TM</sup> Core DSP-related Latencies and Repeat Rates

| Opcode                                                         | Latency | Repeat Rate |

|----------------------------------------------------------------|---------|-------------|

| Multiply and dot-product without saturation after accumulation | 5       | 1           |

| Multiply and dot-product with saturation after accumulation    | 5       | 2           |

| Multiply without accumulation                                  | 5       | 1           |

## System Control Coprocessor (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation and cache protocols, the exception control system, the processor's diagnostic capability, the operating modes (kernel, user, supervisor, and debug), and whether interrupts are enabled or disabled. Configuration information, such as cache size and associativity, presence of features like MIPS16e or floating point unit, is also available by accessing the CP0 registers, listed in Table 3.

Table 3 Coprocessor 0 Registers in Numerical Order

| Register<br>Number | Register<br>Name    | Function                                     |

|--------------------|---------------------|----------------------------------------------|

| 0                  | Index <sup>3</sup>  | Index into the TLB array.                    |

| 1                  | Random <sup>3</sup> | Randomly generated index into the TLB array. |

Table 3 Coprocessor 0 Registers in Numerical Order

| Table 3 Copiocessoi o Registers in Numericai Order |                       |                                                                          |

|----------------------------------------------------|-----------------------|--------------------------------------------------------------------------|

| Register<br>Number                                 | Register<br>Name      | Function                                                                 |

| 2                                                  | EntryLo0 <sup>3</sup> | Low-order portion of the TLB entry for even-numbered virtual pages.      |

| 3                                                  | EntryLo1 <sup>3</sup> | Low-order portion of the TLB entry for odd-numbered virtual pages.       |

| 4                                                  | Context <sup>1</sup>  | Pointer to page table entry in memory.                                   |

| 5                                                  | PageMask <sup>3</sup> | Control for variable page sizes in TLB entries.                          |

| 6                                                  | Wired <sup>3</sup>    | Controls the number of fixed ("wired") TLB entries.                      |

| 7                                                  | HWREna                | Enables access via the RDHWR instruction to selected hardware registers. |

| 8                                                  | BadVAddr <sup>1</sup> | Reports the address for the most recent address-related exception.       |

| 9                                                  | Count <sup>1</sup>    | Processor cycle count.                                                   |

| 10                                                 | EntryHi <sup>3</sup>  | High-order portion of the TLB entry.                                     |

| 11                                                 | Compare <sup>1</sup>  | Timer interrupt control.                                                 |

| 12                                                 | Status <sup>1</sup>   | Processor status and control.                                            |

| 12                                                 | IntCtl <sup>1</sup>   | Interrupt system status and control.                                     |

| 12                                                 | SRSCtl <sup>1</sup>   | Shadow register set status and control.                                  |

| 12                                                 | SRSMap <sup>1</sup>   | Provides mapping from vectored interrupt to a shadow set.                |

| 13                                                 | Cause <sup>1</sup>    | Cause of last general exception.                                         |

| 14                                                 | EPC <sup>1</sup>      | Program counter at last exception.                                       |

| 15                                                 | PRId                  | Processor identification and revision.                                   |

| 15                                                 | EBASE                 | Exception vector base register.                                          |

| 16                                                 | Config                | Configuration register.                                                  |

| 16                                                 | Config1               | Configuration register 1.                                                |

| 16                                                 | Config2               | Configuration register 2.                                                |

| 16                                                 | Config3               | Configuration register 3.                                                |

| 16                                                 | Config7               | Configuration register 7.                                                |

Table 3 Coprocessor 0 Registers in Numerical Order

| Register<br>Number                                                       | Register<br>Name                | Function                                     |

|--------------------------------------------------------------------------|---------------------------------|----------------------------------------------|

| 17                                                                       | Reserved                        | Reserved in the 24KEc core.                  |

| 18                                                                       | WatchLo <sup>1</sup>            | Low-order watchpoint address.                |

| 19                                                                       | WatchHi <sup>1</sup>            | High-order watchpoint address.               |

| 20-22                                                                    | Reserved                        | Reserved in the 24KEc core.                  |

| 23                                                                       | Debug <sup>2</sup>              | Debug control and exception status.          |

| 23                                                                       | Trace<br>Control <sup>2</sup>   | PC/Data trace control register.              |

| 23                                                                       | Trace<br>Control2 <sup>2</sup>  | Additional PC/Data trace control.            |

| 23                                                                       | User Trace<br>Data <sup>2</sup> | User Trace control register.                 |

| 23                                                                       | TraceBPC <sup>2</sup>           | Trace breakpoint control.                    |

| 24                                                                       | DEPC <sup>2</sup>               | Program counter at last debug exception.     |

| 25                                                                       | PerfCount                       | Performance counters and associated control. |

| 26                                                                       | ErrCtl                          | Used for software testing of cache arrays.   |

| 27                                                                       | CacheErr                        | Cache parity error interface.                |

| 28                                                                       | TagLo/<br>DataLo                | Low-order portion of cache tag interface.    |

| 29                                                                       | DataHi                          | Hi-order portion of cache tag interface.     |

| 30                                                                       | ErrorEPC <sup>1</sup>           | Program counter at last error.               |

| 31                                                                       | DESAVE <sup>2</sup>             | Debug handler scratchpad register.           |

| Registers used in exception processing.     Registers used during debug. |                                 |                                              |

- 2. Registers used during debug.

- 3. Registers used in memory management.

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including boundary cases in data, external events, or program errors. Table 4 shows the exception types in order of priority.

Table 4 24KEc<sup>TM</sup> Core Exception Types

| Exception             | Description                                                                                                                              |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|

| Reset                 | Assertion of SI_Reset signal.                                                                                                            |  |

| DSS                   | EJTAG Debug Single Step.                                                                                                                 |  |

| DINT                  | EJTAG Debug Interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input, or by setting the EjtagBrk bit in the ECR register. |  |

| DDBLImpr/<br>DDBSImpr | Debug Data Break Load/Store<br>Imprecise                                                                                                 |  |

| NMI                   | Assertion of SI_NMI signal.                                                                                                              |  |

| Interrupt             | Assertion of unmasked hardware or software interrupt signal.                                                                             |  |

| Deferred Watch        | Deferred Watch (unmasked by K DM->!(K DM) transition).                                                                                   |  |

| DIB                   | EJTAG debug hardware instruction break matched.                                                                                          |  |

| WATCH                 | A reference to an address in one of the watch registers (fetch).                                                                         |  |

| AdEL                  | Fetch address alignment error. Fetch reference to protected address.                                                                     |  |

| TLBL                  | Fetch TLB miss.                                                                                                                          |  |

| TLBL                  | Fetch TLB hit to page with V=0.                                                                                                          |  |

| I Cache Error         | Instruction cache parity error                                                                                                           |  |

| IBE                   | Instruction fetch bus error.                                                                                                             |  |

| DBp                   | EJTAG Breakpoint (execution of SDBBP instruction).                                                                                       |  |

| Sys                   | Execution of SYSCALL instruction.                                                                                                        |  |

| Вр                    | Execution of BREAK instruction.                                                                                                          |  |

| CpU                   | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                            |  |

| CEU                   | Execution of a CorExtend instruction when CorExtend is not enabled.                                                                      |  |

| DSPDis                | DSP ASE State Disabled.                                                                                                                  |  |

| RI                    | Execution of a Reserved Instruction.                                                                                                     |  |

| C2E                   | Coprocessor2 Exception                                                                                                                   |  |

| IS1                   | Implementation specific Coprocessor2 exception                                                                                           |  |

Table 4 24KEc<sup>TM</sup> Core Exception Types (Continued)

| Exception     | Description                                                         |

|---------------|---------------------------------------------------------------------|

| Ov            | Execution of an arithmetic instruction that overflowed.             |

| Tr            | Execution of a trap (when trap condition is true).                  |

| Machine Check | TLB write that conflicts with an existing entry.                    |

| DDBL / DDBS   | EJTAG Data Address Break (address only).                            |

| WATCH         | A reference to an address in one of the watch registers (data).     |

| AdEL          | Load address alignment error.  Load reference to protected address. |

| AdES          | Store address alignment error. Store to protected address.          |

| TLBL          | Load TLB miss.                                                      |

| TLBL          | Load TLB hit to page with V=0.                                      |

| TLBS          | Store TLB miss.                                                     |

| TLBS          | Store TLB hit to page with V=0.                                     |

| TLB Mod       | Store to TLB page with D=0.                                         |

| D Cache Error | Data cache parity error - imprecise                                 |

| DBE           | Load or store bus error - imprecise                                 |

### **Interrupt Handling**

The 24KEc core includes support for six hardware interrupt pins, two software interrupts, a timer interrupt, and a performance counter interrupt. These interrupts can be used in any of three interrupt modes, as defined by Release 2 of the MIPS32 Architecture:

- Interrupt compatibility mode, which acts identically to that in an implementation of Release 1 of the Architecture.

- Vectored Interrupt (VI) mode, which adds the ability to

prioritize and vector interrupts to a handler dedicated

to that interrupt, and to assign a GPR shadow set for

use during interrupt processing. The presence of this

mode is denoted by the VInt bit in the *Config3* register.

This mode is architecturally optional; but it is always

present on the 24KEc core, so the VInt bit will always

read as a 1 for the 24KEc core.

External Interrupt Controller (EIC) mode, which

redefines the way in which interrupts are handled to

provide full support for an external interrupt controller

handling prioritization and vectoring of interrupts. This

presence of this mode denoted by the VEIC bit in the

Config3 register. Again, this mode is architecturally

optional. On the 24KEc core, the VEIC bit is set

externally by the static input, SI\_EICPresent, to allow

system logic to indicate the presence of an external

interrupt controller.

The reset state of the processor is to interrupt compatibility mode such that a processor supporting Release 2 of the Architecture, like the 24KEc core, is fully compatible with implementations of Release 1 of the Architecture.

VI or EIC interrupt modes can be combined with the optional shadow registers to specify which shadow set should be used upon entry to a particular vector. The shadow registers further improve interrupt latency by avoiding the need to save context when invoking an interrupt handler.

## **GPR Shadow Registers**

Release 2 of the MIPS32 Architecture optionally removes the need to save and restore GPRs on entry to high priority interrupts or exceptions, and to provide specified processor modes with the same capability. This is done by introducing multiple copies of the GPRs, called *shadow sets*, and allowing privileged software to associate a shadow set with entry to kernel mode via an interrupt vector or exception. The normal GPRs are logically considered shadow set zero.

The number of GPR shadow sets is a build-time option on the 24KEc core. Although Release 2 of the Architecture defines a maximum of 16 shadow sets, the core allows one (the normal GPRs), two, or four shadow sets. The highest number actually implemented is indicated by the SRSCtl $_{\rm HSS}$  field. If this field is zero, only the normal GPRs are implemented.

Shadow sets are new copies of the GPRs that can be substituted for the normal GPRs on entry to kernel mode via an interrupt or exception. Once a shadow set is bound to a kernel mode entry condition, reference to GPRs work exactly as one would expect, but they are redirected to registers that are dedicated to that condition. Privileged software may need to reference all GPRs in the register file, even specific shadow registers that are not visible in the current mode. The RDPGPR and WRPGPR instructions are used for this purpose. The CSS field of the *SRSCtl*

register provides the number of the current shadow register set, and the PSS field of the *SRSCtl* register provides the number of the previous shadow register set (that which was current before the last exception or interrupt occurred).

If the processor is operating in VI interrupt mode, binding of a vectored interrupt to a shadow set is done by writing to the *SRSMap* register. If the processor is operating in EIC interrupt mode, the binding of the interrupt to a specific shadow set is provided by the external interrupt controller, and is configured in an implementation-dependent way. Binding of an exception or non-vectored interrupt to a shadow set is done by writing to the ESS field of the *SRSCtl* register. When an exception or interrupt occurs, the value of SRSCtl<sub>CSS</sub> is copied to SRSCtl<sub>PSS</sub>, and SRSCtl<sub>CSS</sub> is set to the value taken from the appropriate source. On an ERET, the value of SRSCtl<sub>PSS</sub> is copied back into SRSCtl<sub>CSS</sub> to restore the shadow set of the mode to which control returns.

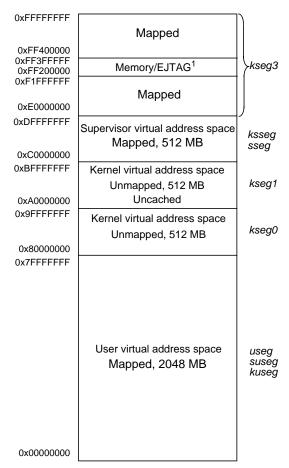

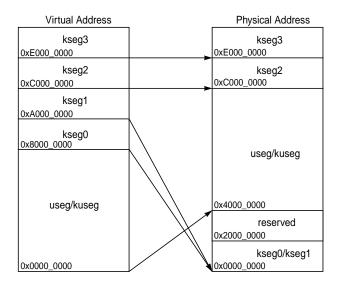

# **Modes of Operation**

The 24KEc core supports four modes of operation: user mode, supervisor mode, kernel mode, and debug mode. User mode is most often used for application programs. Supervisor mode gives an intermediate privilege level with access to the ksseg address space. Supervisor mode is not supported with the fixed mapping MMU. Kernel mode is typically used for handling exceptions and operating system kernel functions, including CP0 management and I/O device accesses. An additional Debug mode is used during system bring-up and software development. Refer to "EJTAG Debug Support" on page 24 for more information on debug mode.

This space is mapped to memory in kernel mode, and by the EJTAG module in debug mode.

Figure 3 24KEc<sup>TM</sup> Core Virtual Address Map

## **Memory Management Unit (MMU)**

The 24KEc core contains a configurable Memory Management Unit (MMU) that is primarily responsible for converting virtual addresses to physical addresses and providing attribute information for different segments of memory.

Two types of MMUs are possible on the 24KEc core, selectable when the core is synthesized. Software can identify the type of MMU present by querying the MT field of the *Config* register.

Translation Lookaside Buffer (TLB) -style MMU.

The basic TLB functionality is specified by the MIPS32 Privileged Resource Architecture (PRA). A TLB provides mapping and protection capability with

- per-page granularity. The 24KEc implementation allows a wide range of page sizes to be present simultaneously.

- 2. Fixed Mapping Translation (FMT) -style MMU. The FMT is much simpler and smaller than the TLB-style MMU, and is a good choice when the full protection and flexibility of the TLB is not needed.

### Translation Lookaside Buffer (TLB)

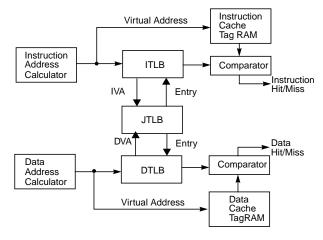

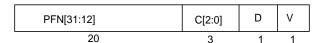

The TLB consists of three address translation buffers:

- 16/32/64 dual-entry fully associative Joint TLB (JTLB)

- 4-entry fully associative Instruction Micro TLB (ITLB)

- 8-entry fully associative Data Micro TLB (DTLB)

When an instruction or data address is calculated, the virtual address is compared to the contents of the appropriate micro TLB (uTLB). If the address is not found in the ITLB or DTLB, the JTLB is accessed. If the entry is found in the JTLB, that entry is then written into the uTLB. If the address is not found in the JTLB, a TLB exception is taken.

Figure 4 shows how the ITLB, DTLB, and JTLB are implemented in the 24KEc core.

Figure 4 Address Translation During a Cache Access

## Joint TLB (JTLB)

The 24KEc core implements a fully associative JTLB containing 16, 32, or 64-dual-entries mapping up to 128 virtual pages to their corresponding physical addresses. The purpose of the TLB is to translate virtual addresses and their corresponding ASIDs into a physical memory

address. The translation is performed by comparing the upper bits of the virtual address (along with the ASID) against each of the entries in the *tag* portion of the joint TLB structure.

The JTLB is organized as pairs of even and odd entries containing pages that range in size from 4 KB to 256 MB, in factors of four, into the 4 GB physical address space. The JTLB is organized in page pairs to minimize the overall size. Each *tag* entry corresponds to two data entries: an even page entry and an odd page entry. The highest order virtual address bit not participating in the tag comparison is used to determine which of the data entries is used. Since page size can vary on a page-pair basis, the determination of which address bits participate in the comparison and which bit is used to make the even-odd determination is decided dynamically during the TLB look-up.

### **Instruction TLB (ITLB)**

The ITLB is a small 4-entry, fully associative TLB dedicated to performing translations for the instruction stream. The ITLB only maps 4 KB or 1 MB pages/ subpages. For 4 KB or 1 MB pages, the entire page is mapped in the ITLB. If the main TLB page size is between 4 KB and 1 MB, only the current 4 KB subpage is mapped. Similarly, for page sizes larger than 1 MB, the current 1 MB subpage is mapped.

The ITLB is managed by hardware and is transparent to software. The larger JTLB is used as a backing structure for the ITLB. If a fetch address cannot be translated by the ITLB, the JTLB is used to attempt to translate it in the following clock cycle, or when available. If successful, the translation information is copied into the ITLB for future use. There is a minimum two cycle ITLB miss penalty.

### Data TLB (DTLB)

The DTLB is a small 8-entry, fully associative TLB dedicated to performing translations for loads and stores. Similar to the ITLB, the DTLB only maps either 4 KB or 1 MB pages/subpages.

The DTLB is managed by hardware and is transparent to software. The larger JTLB is used as a backing structure for the DTLB. If a load/store address cannot be translated by the DTLB, a lookup is done in the JTLB. If the JTLB translation is successful, the translation information is copied into the DTLB for future use. The DTLB miss penalty is also two cycles.

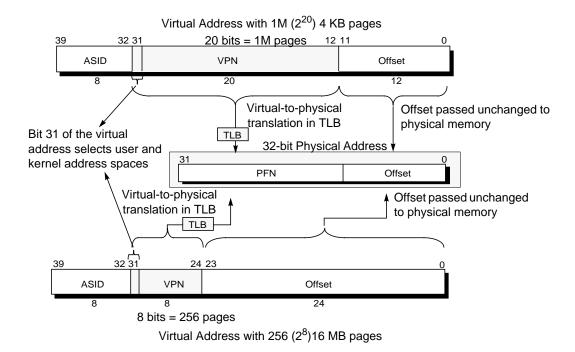

Figure 5 32-bit Virtual Address Translation

### Virtual-to-Physical Address Translation

Converting a virtual address to a physical address begins by comparing the virtual address from the processor with the virtual addresses in the TLB; there is a match when the virtual page number (VPN) of the address is the same as the VPN field of the entry, and either:

- The Global (G) bit of the TLB entry is set, or

- The ASID field of the virtual address is the same as the ASID field of the TLB entry.

This match is referred to as a TLB *hit*. If there is no match, a TLB *miss* exception is taken by the processor and software is allowed to refill the TLB from a page table of virtual/physical addresses in memory.

Figure 5 shows a flow diagram of the address translation process for two different page sizes.

The top portion of Figure 5 shows a virtual address for a 4 KB page size. The width of the *Offset* in Figure 5 is defined by the page size. The remaining 20 bits of the address represent the virtual page number (*VPN*), and index the 1M-entry page table.

The bottom portion of Figure 5 shows the virtual address for a 16 MB page size. The remaining 8 bits of the address represent the VPN, and index the 256-entry page table.

In Figure 5, the virtual address is extended with an 8-bit address space identifier (ASID), which reduces the frequency of TLB flushes during context switches. This 8-bit ASID contains the number assigned to that process and is stored in the CP0 *EntryHi* register.

### Hits, Misses, and Multiple Matches

Each JTLB entry contains a tag portion and a data portion. If a match is found, the upper bits of the virtual address are replaced with the page frame number (PFN) stored in the corresponding entry in the data array of the joint TLB (JTLB). The granularity of JTLB mappings is defined in terms of TLB *pages*. The 24KEc core's JTLB supports pages of different sizes ranging from 4 KB to 256 MB in factors of 4.

Table 5 shows the address bits used for even/odd bank selection depending on page size and the relationship between the legal values in the mask register and the selected page size.

Table 5 Mask and Page Size Values

| Pagemask[28:13]   | Page Size | Even/Odd Bank<br>Select Bit |

|-------------------|-----------|-----------------------------|

| 00000000000000000 | 4KB       | VAddr[12]                   |

| 000000000000011   | 16KB      | VAddr[14]                   |

| 000000000001111   | 64KB      | VAddr[16]                   |

| 000000000111111   | 256KB     | VAddr[18]                   |

| 0000000011111111  | 1MB       | VAddr[20]                   |

| 0000001111111111  | 4MB       | VAddr[22]                   |

| 0000111111111111  | 16MB      | VAddr[24]                   |

| 0011111111111111  | 64MB      | VAddr[26]                   |

| 11111111111111111 | 256MB     | VAddr[28]                   |

If no match occurs (TLB miss), an exception is taken and software refills the TLB from the page table resident in memory. Software can write over a selected TLB entry or use a hardware mechanism to write into a random entry.

The 24KEc core implements a TLB write compare mechanism to ensure that multiple TLB matches do not occur. On the TLB write operation, the write value is compared with all other entries in the TLB. If a match occurs, the 24KEc core takes a machine check exception, sets the TS bit in the CPO *Status* register, and aborts the write operation.

Compared with previous cores from MIPS Technologies, the 24KEc core uses a more relaxed check for multiple matches in order to avoid machine check exceptions while flushing or initializing the TLB. On a write, all matching entries are disabled to prevent them from matching on future compares. A machine check is only signaled if the entry being written has its valid bit set, the matching entry in the TLB has its valid bit set, and the matching entry is not the entry being written.

### **TLB Tag and Data Formats**

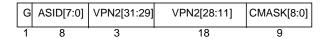

Figure 6 shows the format of a TLB *tag* entry. The entry is divided into the follow fields:

- · Global process indicator

- · Address space identifier

- Virtual page number

- · Compressed page mask

Setting the global process indicator (G bit) indicates that the entry is global to all processes and/or threads in the system. In this case, the 8-bit address space identifier (ASID) value is ignored since the entry is not relative to a specific thread or process.

The ASID field can help to reduce the frequency of TLB flushes on a context switches. The existence of the ASID allows multiple processes to exist in both the TLB and instruction caches. The current ASID value is stored in the *EntryHi* register and is compared to the ASID value of each entry. Figure 6 and Table 6 show the TLB tag entry format.

Figure 6 TLB Tag Entry Format

Table 6 TLB Tag Entry Fields

| Field Name                  | Description                                                                                                                                                                                                                                                                      |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G                           | Global Bit. When set, indicates that this entry is global to all processes and/or threads and thus disables inclusion of the ASID in the comparison.                                                                                                                             |

| ASID[7:0]                   | Address Space Identifier. Identifies with which process or thread this TLB entry is associated.                                                                                                                                                                                  |

| VPN2[31:29],<br>VPN2[28:13] | Virtual Page Number divided by 2. This field contains the upper bits of the virtual page number. Because it represents a pair of TLB pages, it is divided by 2. Bits 31:29 are always included in the TLB lookup comparison. Bits 28:13 are included depending on the page size. |

| CMASK[8:0]                  | Compressed page mask value. This field is a compressed version of the page mask. It defines the page size by masking the appropriate VPN2 bits from being involved comparison. It is also used to determine which address bit is used to make the even-odd page determination.   |

Figure 7 and Table 7 show the TLB data array entry format.

Figure 7 TLB Data Array Entry Format

Table 7 TLB Data Array Entry Fields

| Field Name | Description                                                                                                                                                                                                                              |                                                           |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|

| PFN[31:12] | Physical Frame Number. Defines the upper bits of the physical address.  For page sizes larger than the 4KB, only a subset of these bits is actually used.                                                                                |                                                           |  |

|            | Cacheability. Contains an encoded value of the cacheability attributes and determines whether the page should be placed in the cache or not. The field is encoded as follows:                                                            |                                                           |  |

|            | CS[2:0]                                                                                                                                                                                                                                  | Coherency Attribute                                       |  |

|            | 0                                                                                                                                                                                                                                        | Cacheable, noncoherent, write through, no write allocate. |  |

|            | 1                                                                                                                                                                                                                                        | Reserved                                                  |  |

| GF2 OI     | 2                                                                                                                                                                                                                                        | Uncached                                                  |  |

| C[2:0]     | 3                                                                                                                                                                                                                                        | Cacheable, noncoherent, write back, write allocate        |  |

|            | 4-6                                                                                                                                                                                                                                      | Reserved                                                  |  |

|            | 7                                                                                                                                                                                                                                        | Uncached Accelerated                                      |  |

|            |                                                                                                                                                                                                                                          |                                                           |  |

| D          | "Dirty" or write-enable bit. Indicates that<br>the page has been written and/or is<br>writable. If this bit is set, stores to the<br>page are permitted. If the bit is cleared,<br>stores to the page cause a TLB Modified<br>exception. |                                                           |  |

| V          | Valid bit. Indicates that the TLB entry, and thus the virtual page mapping, are valid. If this bit is set, accesses to the page are permitted. If the bit is cleared, accesses to the page cause a TLB Invalid exception.                |                                                           |  |

## Page Sizes and Replacement Algorithm

To assist in controlling both the amount of mapped space and the replacement characteristics of various memory regions, the 24KEc core provides two mechanisms. First, the page size can be configured, on a per-entry basis, to map a page size from 4 KB to 256 MB (in multiples of 4). The CP0 *PageMask* register is loaded with the mapping page size, which is then entered into the TLB when a new entry is written. Thus, operating systems can provide special purpose maps. For example, a typical frame buffer might be memory mapped with only one TLB entry.

The second mechanism controls the replacement algorithm when a TLB miss occurs. To select a TLB entry to be written with a new mapping, the 24KEc core provides a random replacement algorithm. However, the processor also provides a mechanism where a programmable number of mappings can be locked into the TLB via the CPO *Wired* register, thus avoiding random replacement.

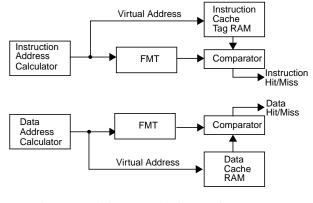

# **Fixed Mapping Translation (FMT)**

The 24KEc core optionally provides a Fixed Mapping Translation mechanism that is smaller and simpler than the full Translation Lookaside Buffer (TLB). Like a TLB, the FMT performs virtual-to-physical address translation and provides attributes for the different segments. Those segments that are unmapped in a TLB implementation (kseg0 and kseg1) are handled identically by the FMT.

Figure 8 shows how the FMT is implemented in the 24KEc core.

Figure 8 Address Translation During Access

In general, the FMT also determines the cacheability of each segment. These attributes are controlled via bits in the *Config* register. Table 8 shows the encoding for the K23 (bits 30:28), KU (bits 27:25), and K0 (bits 2:0) fields of the

Config register. Table 9 shows how the cacheability of the virtual address segments is controlled by these fields.

Table 8 Cache Coherency Attributes

| Config Register Fields<br>K23, KU, and K0 | Cache Coherency Attribute                                    |

|-------------------------------------------|--------------------------------------------------------------|

| 0                                         | Cacheable, noncoherent, write-<br>through, no write-allocate |

| 1                                         | Reserved                                                     |

| 2                                         | Uncached                                                     |

| 3                                         | Cacheable, noncoherent, write-<br>back, write-allocate       |

| 4-6                                       | Reserved                                                     |

| 7                                         | Uncached Accelerated                                         |

In a 24KEc core with FMT, no translation exceptions can be taken, although address errors are still possible.

Table 9 Virtual Address Segments

| Segment       | Virtual<br>Address<br>Range | Cacheability                                                                                                                           |

|---------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| useg<br>kuseg | 0x0000_0000-<br>0x7FFF_FFFF | Controlled by the KU field (bits 27:25) of the Config register. See Table 8 for mapping. This segment is always uncached when ERL = 1. |

| kseg0         | 0x8000_0000-<br>0x9FFF_FFFF | Controlled by the K0 field (bits 2:0) of the Config register. See Table 8 for mapping.                                                 |

| kseg1         | 0xA000_0000-<br>0xBFFF_FFFF | Always uncacheable.                                                                                                                    |

| kseg2         | 0xC000_0000-<br>0xDFFF_FFFF | Controlled by the K23 field (bits 30:28) of the Config register. See Table 8 for mapping.                                              |

| kseg3         | 0xE000_0000-<br>0xFFFF_FFFF | Controlled by the K23 field (bits 30:28) of the Config register. See Table 8 for mapping.                                              |

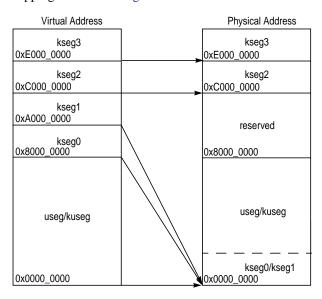

The FMT performs a simple translation to map from virtual addresses to physical addresses. This mapping is shown in Figure 9.

Figure 9 FMT Memory Map (ERL=0) in the 24KEc<sup>TM</sup> Core

When ERL=1, useg and kuseg become unmapped (virtual address is identical to the physical address) and uncached. This behavior is the same as if there was a TLB. This mapping is shown in Figure 10.

Figure 10 FMT Memory Map (ERL=1) in the  $24KEc^{TM}$  Core

# **Instruction Cache**

The instruction cache is an on-chip memory block of 0/8/16/32/64 KB, with 4-way associativity. Because the instruction cache is virtually indexed, the virtual-to-physical address translation occurs in parallel with the

cache access rather than having to wait for the physical address translation. A tag entry holds 20 bits of physical address, a valid bit, a lock bit, and an optional parity bit per way. The instruction data entry holds two instructions (64 bits) per way, as well as 6 bits of pre-decode information to speed the decode of branch and jump instructions, and 9 optional parity bits (one per data byte plus one more for the pre-decode information). The LRU replacement bits (6b) are stored in a separate array.

The instruction cache block also contains and manages the instruction line fill buffer. Besides accumulating data to be written to the cache, instruction fetches that reference data in the line fill buffer are serviced either by a bypass of that data, or data coming from the external interface. The instruction cache control logic controls the bypass function.

The 24KEc core supports instruction-cache locking. Cache locking allows critical code or data segments to be locked into the cache on a "per-line" basis, enabling the system programmer to maximize the efficiency of the system cache.

The cache-locking function is always available on all instruction-cache entries. Entries can then be marked as locked or unlocked on a per entry basis using the CACHE instruction.

### **Data Cache**

The data cache is an on-chip memory block of 0/8/16/32/64 KB, with 4-way associativity. Since the data cache is virtually indexed, the virtual-to-physical address translation occurs in parallel with the cache access. A tag entry holds 20 bits of physical address, a valid bit, a lock bit, and an optional parity bit per way. The data entry holds 64 bits of data per way, with optional parity per byte. There is an additional array holding dirty bits and LRU replacement algorithm bits (6b LRU, 4b dirty, and optionally 4b dirty parity).

Using 4KB pages in the TLB and 32 or 64KB cache sizes it is possible to get virtual aliasing. A single physical address can exist in multiple cache locations if it was accessed via different virtual addresses. For a 32KB data cache, there is an implementation option to eliminate virtual aliasing. If this option is not selected, or a 64KB cache is implemented, software must take care of any aliasing issues by using a page coloring scheme or some other mechanism.

In addition to instruction-cache locking, the 24KEc core also supports a data-cache locking mechanism identical to the instruction cache. Critical data segments are locked into the cache on a "per-line" basis. The locked contents can be updated on a store hit, but will not be selected for replacement on a cache miss.

The cache-locking function is always available on all data cache entries. Entries can then be marked as locked or unlocked on a per-entry basis using the CACHE instruction.

# **Cache Memory Configuration**

The 24KEc core incorporates on-chip instruction and data caches that are usually implemented from readily available single-port synchronous SRAMs and accessed in two cycles: one cycle for the actual SRAM read and another cycle for the tag comparison, hit determination, and way selection. The instruction and data caches each have their own 64-bit data paths and can be accessed simultaneously. Table 10 lists the 24KEc core instruction and data cache attributes.

Table 10 24KEc<sup>TM</sup> Core Instruction and Data Cache Attributes

| Parameter                      | Instruction                | Data                                                                 |

|--------------------------------|----------------------------|----------------------------------------------------------------------|

| Size                           | 0, 8, 16, 32, or 64<br>KB* | 0, 8, 16, 32, or 64<br>KB                                            |

| Organization                   | 4 way set associative      | 4 way set associative                                                |

| Line Size                      | 32 Bytes*                  | 32 Bytes                                                             |

| Read Unit                      | 64 bits*                   | 64 bits                                                              |

| Write Policies                 | N/A                        | write-through without write allocate, write-back with write allocate |

| Miss restart after transfer of | miss word                  | miss word                                                            |

| Cache Locking                  | per line                   | per line                                                             |

<sup>\*</sup>Logical size of instruction cache. Cache physically contains some extra bits used for precoding the instruction type.

## **Cache Protocols**

The 24KEc core supports the following cache protocols:

I

- Uncached: Addresses in a memory area indicated as uncached are not read from the cache. Stores to such addresses are written directly to main memory, without changing cache contents.

- Write-through, no write allocate: Loads and instruction fetches first search the cache, reading main memory only if the desired data does not reside in the cache. On data store operations, the cache is first searched to see if the target address is cache resident. If it is resident, the cache contents are updated, and main memory is also written. If the cache look-up misses, only main memory is written.

- Write-back, write allocate: Stores that miss in the cache will cause a cache refill. Store data, however, is only written to the cache. Caches lines that are written by stores will be marked as dirty. If a dirty line is selected for replacement, the cache line will be written back to main memory.

• Uncached Accelerated: Like uncached, data is never loaded into the cache. Store data can be gathered in a write buffer before being sent out on the bus as a bursted write. This is more efficient than sending out individual writes as occurs in regular uncached mode.

## **Bus Interface (BIU)**

The Bus Interface Unit (BIU) controls the external interface signals. The primary interface implements the Open Core Protocol (OCP). Additionally, the BIU includes a write buffer.

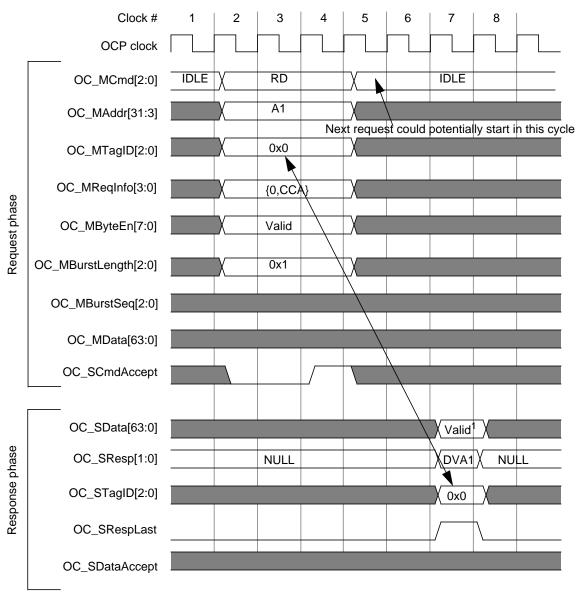

# **OCP Interface**

Table 11 shows the OCP Performance Report for the 24KEc core. This table lists characteristics about the core and the specific OCP functionality that is supported.

Table 11 OCP Performance Report

| Core name                                | 24KEc                                                                                                              |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Core Identity                            | TBD                                                                                                                |

| Vendor Code                              | TBD                                                                                                                |

| Core Code                                | 0x93, visible in ProcessorID field of CP0 <i>PrID</i> register                                                     |

| Revision Code                            | Visible in Revision field of <i>PrID</i> register                                                                  |

| Process dependent                        | No                                                                                                                 |

| Frequency range for this core            | Synthesizable, so varies based on process, libraries, and implementation                                           |

| Area                                     | Synthesizable, so varies based on process, libraries, and implementation                                           |

| Power Estimate                           | Synthesizable, so varies based on process, libraries, and implementation                                           |

| Special reset requirements               | No                                                                                                                 |

| Number of Interfaces                     | 1 OCP master, 2 OCP slave (DMA access for SPRAMs)                                                                  |

| Interface Information:                   |                                                                                                                    |

| Name                                     | OCPMasterInterface                                                                                                 |

| • Type                                   | Master                                                                                                             |

| Master OCP Interface                     |                                                                                                                    |

| a. Operations issued                     | RD, WR                                                                                                             |

| b. Issue rate (per OCP cycle)            | One per cycle, for all of the types listed above except for a non-standard RD (SYNC) which depends on ack latency. |

| Maximum number of operations outstanding | 6 read operations. All writes are posted, so the OCP fabric determines the maximum number of outstanding writes.   |

| Burst support and effect on issue rates  | Fixed burst length of four 64b beats with single request per burst. Burst sequences of WRAP or XOR supported.      |

Table 11 OCP Performance Report

| High level flow control                         | None                                                                                                                                                                                                                                           |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of tags supported and use of those tags  | Total of 8 tags: 6 tags for outstanding RD's, 1 tag for WR & 1 tag for SYNC                                                                                                                                                                    |

| Connection ID and use of connection information | None                                                                                                                                                                                                                                           |

| Use of sideband signals                         | None                                                                                                                                                                                                                                           |

|                                                 | 1. MReqInfo handled in a user defined way. 3 bits used to send cacheable attribute information or encode type of L2 CACHE instruction, 1 bit used to signify SYNC.                                                                             |

| Implementation restrictions                     | 2. MAddrSpace is used (2 bits) to indicate L2/L3 access.                                                                                                                                                                                       |

| restrictions                                    | 4. Core clock is synchronous but a multiple of the OCP clock. The ratios supported are 1:1, 1:1.5, 1:2, 1:2.5, 1:3, 1:3.5, 1:4 and 1:5. A helper pulse is required by the core to transfer data from/to the OCP interface without any hazards. |

| Interface Information:                          |                                                                                                                                                                                                                                                |

| • Name                                          | OCPSlaveInterface                                                                                                                                                                                                                              |

| • Type                                          | Slave                                                                                                                                                                                                                                          |

| Slave OCP Interfaces (DM                        | (A interface to scratchpad)                                                                                                                                                                                                                    |

| a. Operations accepted                          | RD, WR                                                                                                                                                                                                                                         |

| b. Issue rate (per OCP cycle)                   | One per cycle, for all of the types listed above except for a non-standard RD (SYNC) which is not supported.                                                                                                                                   |

| Maximum number of operations outstanding        | 2 outstanding operations which includes both RD & WR.                                                                                                                                                                                          |

| Burst support                                   | Burst access is not supported                                                                                                                                                                                                                  |

| High level flow control                         | Back pressure from slave on data and command accept. Slave assumes no back pressure from the master.                                                                                                                                           |

| Number of tags supported and use of those tags  | Total of 8 tags. Any tag number can be used for read and write operation.                                                                                                                                                                      |

| Connection ID and use of connection information | None                                                                                                                                                                                                                                           |

| Use of sideband signals                         | None                                                                                                                                                                                                                                           |

| Implementation restrictions                     | The slave interface operates at the same clock ratio as that of the master OCP interface.                                                                                                                                                      |

### Write Buffer

The BIU contains a merging write buffer. The purpose of this buffer is to store and combine write transactions before issuing them to the external interface. The write buffer is organized as four 32-byte buffers. Each buffer contains data from a single 32-byte aligned block of memory.

# Write Through

When using the write-through cache policy, the write buffer significantly reduces the number of write transactions on

the external interface and reduces the amount of stalling in the core due to issuance of multiple writes in a short period of time.

# Write Back

The write buffer also holds eviction data for write-back lines. The load-store unit opportunistically pulls dirty data from the cache and sends it to the BIU. It is gathered in the write buffer and sent out as a bursted write.

#### Uncached Accelerated

For uncached accelerated references, the write buffer can gather multiple writes together and then perform a bursted write to increase the efficiency of the bus. Uncached accelerated gathering is supported for word and double word stores only.

Gathering of uncached accelerated stores will start on cache-line aligned addresses, i.e. 32 byte aligned addresses. Uncached accelerated word or double word stores that do not to meet the conditions required to start gathering will be treated like regular uncached stores.

Once an uncached accelerated store meets the requirements needed to start gathering, a gather buffer is reserved for this store. All subsequent uncached accelerated word or double word stores to the same 32B region will write sequentially into this buffer, independent of the word address associated with these latter stores. The uncached accelerated buffer is tagged with the address of the first store.

An uncached accelerated buffer is written to memory (flushed) if:

- 1. The last word in the 32-byte entry being gathered is written. (Implicit flush).

- 2. A PREF Nudge which matches the address associated with the gather buffer (Explicit flush).

- 3. A SYNC instruction is executed. (Explicit flush).

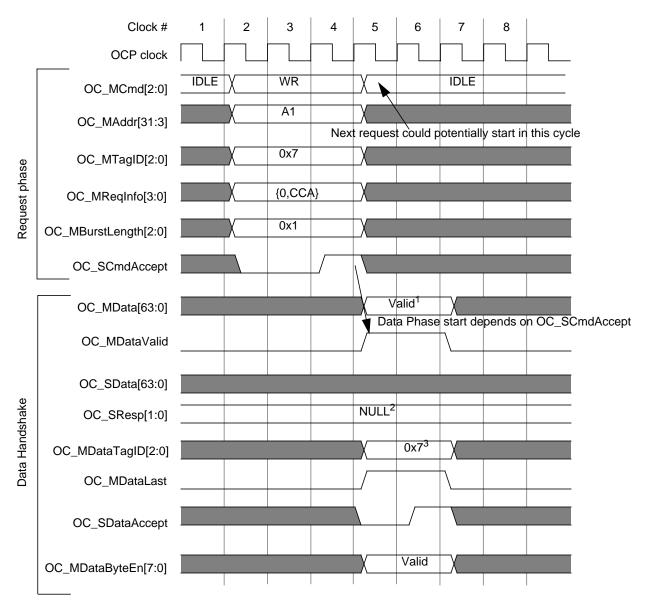

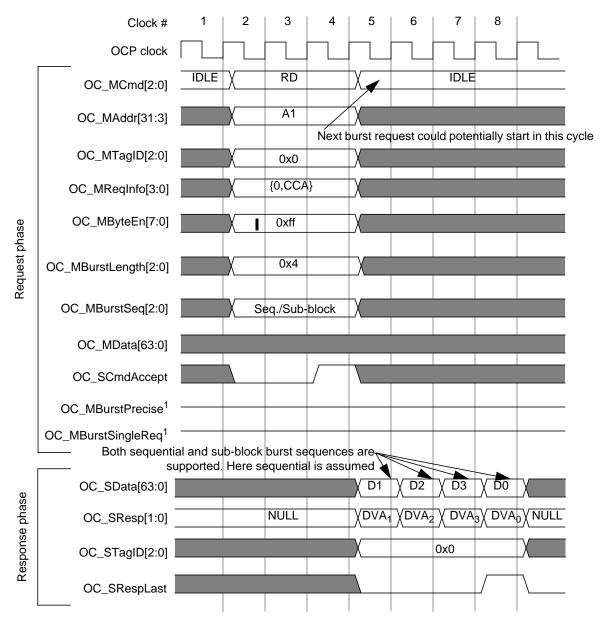

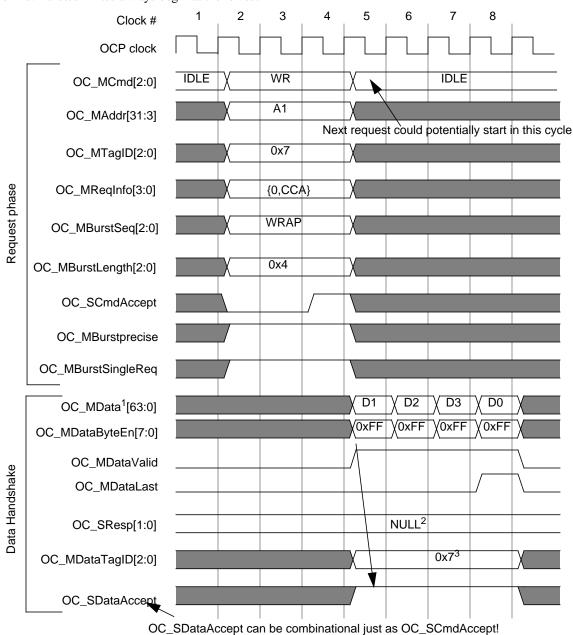

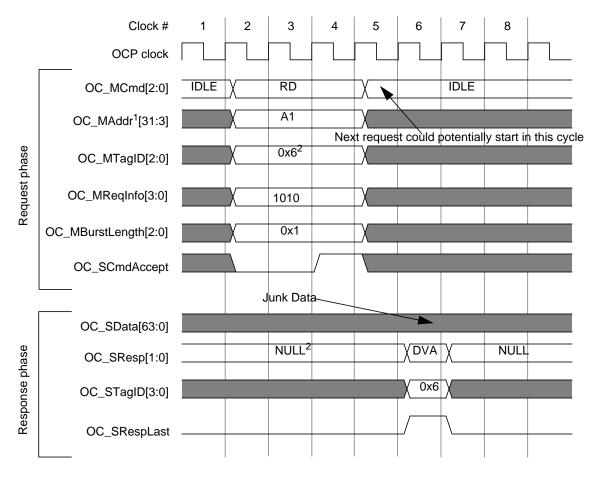

- 4. Bits <31:5> of the address of a Load instruction match the address associated with the gather buffer. (Implicit flush)